為了擴展數控系統邏輯功能的可編程能力,通常在數控系統中配置PLC功能。并采用獨立PLC或內置式PLC兩種方式。但目前內置式PLC一般使用軟件實現。有一套特有的編程與配置方法,這對使用者熟悉新功能提出了額外的要求。現場可編程邏輯器件FPGA具有很強的在線邏輯編程能力。常被應用于實現某些邏輯控制中。比如交通信號燈控制:近來也有用FPGA實現PLC的嘗試。即將與需要實現的控制功能對應的梯形圖直接做成FPGA硬連線邏輯。但這些應用都沒有脫離FPGA本身的現場可編程特性。用戶如需修改控制邏輯。就需要掌握VHDL語言及FPGA的EDA設計方法。否則不能提供更加友好、通用的PLC編程界面。

本文介紹了一種新的數控系統中內置式PLC的FPGA實現方法。它能較好地解決上述技術難題,也便于實際應用。

1 基于ARM和FPGA的數控系統

機床數控系統由控制系統、伺服驅動系統和伺服電機組成。控制系統生成的坐標軸運動指令,被發送到伺服驅動系統。然后由伺服驅動系統形成伺服電機的運轉控制令。從而使伺服電機完成相應的動作。

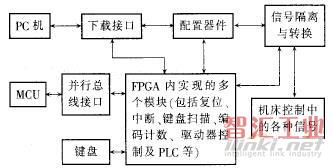

圖1是基于ARM+FPGA的數控系統的FPGA部分結構框圖,下載接口、配置器件及FPGA 3個部分組成了FPGA自身的開發調試環境。可以方便地與PC組成開發調試平臺。機床控制單元MCU使用32位的ARM嵌入式處理器。運行uC/0S實時操作系統,實現控制系統的大量分析和計算工作。比如G代碼解析,根據加工要求形成坐標軸的運動指令以及數控系統的人機界面等。FPGA除了完成對運動指令進行細插補之外。同時還實現了數控系統鍵盤電路的掃描模塊、編碼計數器模塊和驅動器控制模塊的功能。本文要介紹的數控系統內置式PLC也是在FPGA內部實現的。

圖1 數控系統中的FPGA結構框圖

2 用FPGA實現PLC的軟硬件架構

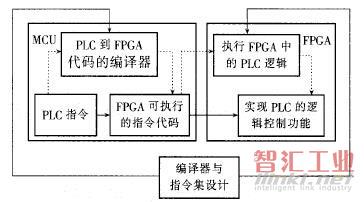

為了有更好的人機界面。更符合工程習慣。采用與主流商業PLC兼容的編程語言進行編程。內置式PLC可以接受最終用戶輸入的PLC指令表(一個特定的子集)。并最終實現相應的邏輯控制功能。FPGA內部是硬件邏輯。顯然無法識別PLC指令,因此,為了實現這種構想。必須設計一套指令集。該指令集定義了FPGA可以執行的最小操作的集合。然后根據指令集來設計編譯器和FPGA內部的PLC邏輯。其軟硬件架構如圖2所示。PLC指令被編譯后,生成FPGA可執行的指令代碼。然后將指令代碼下載到FPGA內部,由執行邏輯對代碼進行逐條執行。最終實現PLC的邏輯控制功能。

圖2 基于FPGA的PLC軟硬件架構

PLC核心邏輯是一個狀態機。可以根據不同的輸入指令執行不同的操作。在設計中。首先應確定需要執行的指令集合,即狀態機的指令集設計。然后根據指令集來設計編譯器和PLC邏輯功能。PLC指令編譯器源程序使用C語言編寫。這樣。此編譯器可以方便地移植到PC、ARM或別的任何支持C編程的平臺上。基于圖2中的軟硬件架構的PLC不能獨立運行。需要MCU對其進行相應的設置和輔助。如圖3所示。在MCU端。需要一個專門處理與PLC接口的任務(對于多任務操作系統)或程序。

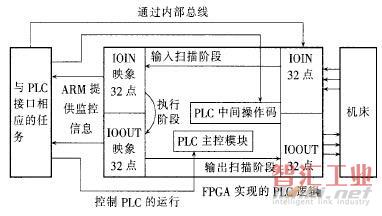

圖3 PLC邏輯的工作過程

在MCU端,可以提供相應的PLC人機界面,提供PLC梯形圖或指令表的編輯、編譯甚至排錯界面,當編譯完成后。生成可供FPGA內部的PLC邏輯執行的“PLC中間操作碼”。當要執行PLC功能時,首先MCU配置FPGA處于“代碼下載狀態”。并由MCU將編譯后的代碼下載到FPGA的RAM中:下載完成后。MCU將FPGA設置為“PLC運行狀態”。開始依次讀入輸入和輸出端口的狀態。并根據所要執行的指令更新狀態。最后輸出刷新狀態。FPGA還有一個“監控狀態”。此時。ARM處理器可以直接設置PLC的輸入輸出10寄存器的值。并可以單步運行PLC中間操作碼。ARM結合返回信息。并配合相應的界面,即實現了對PLC的調試。

3 PLC邏輯的EDA設計方法

新型FPGA器件及新的EDA設計軟件和工具是這種數控系統內置式PLC實現方式的前提。沒有EDA設計流程和方法的支撐。是很難完成相應設計工作的。

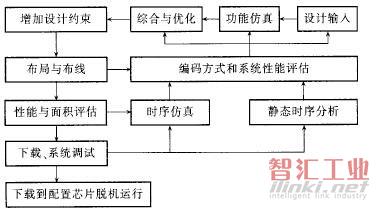

圖4是典型的EDA設計流程。主要包括設計輸入、功能仿真、綜合與優化、映射和布局布線以及最后的下載驗證等環節。EDA設計流程中。最重要的環節便是仿真。因為所設計的對象在FPGA內部很難在硬件上進行測試。必須利用諸如Active—HDL。ModelSim等仿真工具進行功能仿真、綜合后仿真以及布局布線后仿真。設計過程和仿真過程是交叉同步進行的。而且最好設計一個模塊。即對一個模塊的功能進行仿真,確保其正確后,才可以集成到更高層面的設計中去。仿真的主要任務就是檢驗HDL是否能滿足設計所提的要求。檢驗的方式是編寫測試平臺。在測試平臺上給模塊輸入條件。觀察或檢驗其輸出。從而驗證是否滿足設計要求。Active—HDL的Generate TestBench功能還可以生成測試向量的模板。大大加速了設計過程。

圖4 EDA設計流程

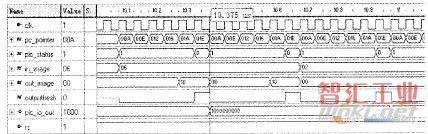

圖5 PLC原型機邏輯仿真結果

總之,掌握并正確使用EDA設計方法。是使用FPGA進行邏輯設計成功的關鍵。

4 在數控系統中的實現與分析

基于FPGA的PLC實現方法在我們自主研發的基于ARM+FPGA的數控系統中得到了應用。形成了PLC原型機,實現了基本的PLC邏輯控制功能。能夠與數控系統集成在一起。結合相應的控制界面。可以對機床的各邏輯開關量進行PLC編程控制。更重要的是。這種框架下的PLC具有開放式結構。可根據需要不斷完善。實現更復雜的功能。如圖5所示,PLC有2個主要狀態。即輸入輸出刷新(pc status=0)和運行狀態(pc status=1)。在pc status=0時,輸入被采樣,輸出映像被置位:當pc status=1時,PLC開始運行,pc pointer為PLC內部指令的指針,在每個時鐘周期,PLC執行一條指令,并將指令指針后移,當執行完所有指令后,outputfresh置高,允許輸出映像寄存器的結果輸出到端口plc io out中去。以上過程反復進行,便實現了PLC的最基本邏輯功能。

針對數控系統中各種內置式PLC的實現方式。基于FPGA的解決方案在以下一些方面做了特別的處理:

(1)復位問題。當FPGA一上電時,其內部的PLC邏輯即令其自身進入了一個自復位狀態。此時如果沒有外部MCU給予正確的操作指令。FPGA將不會進入其他任何狀態。從而確保PLC不會產生任何的誤動作。

(2)響應時間。PLC程序會得到周而復始的執行,當輸入狀態(in image)改變時,輸出狀態會在下一個允許輸出信號有效時(outputfresh=1)得到更新。PLC的最大響應周期取決于所執行的指令條數。對于絕大多數指令而言。PLC可在每個時鐘周期執行一條語句。在最后一條語句執行完成后的下一個時鐘上升沿輸出得到刷新,同時在此刷新時鐘周期內。PLC進行循環復位的初始化工作。最差的情況時。輸入信號在上次采集剛剛結束后發生變化。需要在下一次采樣并執行完成后才能反映到輸出上。即響應時間為Tresponse=(PLC指令條數+1)×2×時鐘周期,本文使用的時鐘周期為50ns,因此有:Tresponse=(PLC指令條數+1)×2×50ns:受FPGA內部的EAB(Embedded Arrav B10ck。一種專門用來綜合成RAM的內部資源)數量的限制。只能綜合出約2k bvte RAM(除非設置必要的控制寄存器)。當執行約有2 000條PLC指令時。最大響應時間為0。2ms量級。

對于一般以軟件方式實現的PLC。多使用一個特定的任務來實現PLC邏輯控制功能。在嵌入式操作系統中。任務的上下文切換時間一般在斗s量級;而且隨著系統中其他任務的就緒。PLC任務將面臨被暫時掛起。在這種情形下。其響應時間將進一步變長。當然。如果使用高頻率運行下的嵌入式處理器(60MHz以上),在指令條數較多時,其響應時間也可接受。但數控系統中的PLC功能一般都只實現對機床的簡單邏輯控制。控制環境比較簡單。指令條數有限。因此使用FPGA方式實現還是有其特有的優勢的。

(3)PLC運行階段的可靠性。PLC是將編譯后的可執行指令放到FPGA內部的RAM中運行。只要完成必要的配置。PLC便完全獨立運行,不再需要外部MCU的干預。換言之,此時。即使MCU死機或程序跑飛,也不會影響正在執行中的PLC功能。因此。使用FPGA來實現PLC功能。對于提高數控系統的整體可靠性是有優勢的。

(4)PLC指令長度的支持。由于FPGA內部的EAB資源有限,因此能夠容納的PLC指令長度有限。同時。每次PLC運行前都必須由MCU將代碼下載到FPGA中。然后才可控制PLC開始運行。即FPGA不能獨自實現PLC功能。為了解決這一問題,可考慮為FPGA專門配置非易失性的存儲器。比如Flash。這樣不但可以擴大PLC指令長度。而且還可實現上電自動運行PLC程序。甚至不需要MCU的輔助和干預,但這將需=要諸如編程器之類的部件的支持。

5 結論與展望

本文敘述了一種新的方法——用FPGA實現數控系統內置式的PLC。并提供對標準PLC編程語言的支持,這是一個在體系結構上的大膽嘗試。用FPGA實現的PLC模塊相當于一個專用處理器。只不過根據PLC的特定應用場合,結合編譯器的設計。可對其指令系統進行靈活的配置和架構的調整。這種實現方法還需要經過長期的應用。才能對其特性進行更廣泛的檢驗:除了應用于數控系統中之外。這種設計方法稍加移植。便可應用于所有需要PLC功能的嵌入式控制環境中。

在現代EDA設計方法下。使用FPGA實現PLC功能是在特定場合下行之有效的方法。隨著EDA技術和EDA工具的發展。可能會出現許多新的思路和方法。比如。如果出現可以直接將PLC程序翻譯成可綜合的VHDL代碼的工具。那就可以既便于一般用戶使用。又能極大地發揮出FPGA的優勢。

(審核編輯: 滄海一土)

分享